# THE INFLUENCE OF THE SiO<sub>2</sub> UNDERLAYER ON THE JOULE HEATING OF AI-Cu-Si METALLIZATION OF SILICON DEVICES

LUBY, Š.,1) NOVÁK, I.,11 ROMAN, P.,21 Bratislava

Experimental conductors were patterned in Al-Cu-Si films deposited by magnetron sputtering onto oxidized silicon substrates with constant as well as with varying SiO<sub>2</sub> thicknesses. The stripes were stressed by high current density (>10<sup>6</sup> A/cm<sup>2</sup>). Under these conditions the temperature increase of the conductors due to Joule heating reached 70°C for the first type of substrate. For the substrate with varying oxide thickness, smaller than or equal to that in the previous case, the mean value of the temperature increase (fluctuating along the conductor) was 37—39°C. The experimental results are compared with calculations of temperature distribution based on a simple model. The agreement is quite good and it indicates that the heating of the metallization is influenced mainly by the thickness of the SiO<sub>2</sub> underlayer, which has the thermal conductivity by two orders of magnitude smaller than silicon. The results show that the Joule heating of conductors stressed by high current densities can significantly influence the operational conditions and reliability of semiconductor devices.

### 1. INTRODUCTION

Electromigration is an important degradation process which adversely influences the reliability and lifetime of the metallization of semiconductor devices. Among the reviews concerning this phenomenon at least that by d'Heurle and Ho should be mentioned [1].

The electromigration performance of the often used Al-Cu-Si conductors of silicon devices and circuits was studied in many papers (e.g. [2, 3, 4]). From our silicon devices and circuits was studied in many papers (e.g. [2, 3, 4]). From our previous results [4, 5, 6] it follows that the Joule heating of Al-based metallization deposited onto a SiO<sub>2</sub> underlayer and stressed during the electromigration lifetime test by the current density  $j \ge 10^6 \text{A/cm}^2$  cannot be omitted. With the usual oxide thickness  $\approx 1 \, \mu \text{m}$  the temperature increase equals some tens of degrees. Consequently, the electromigration failure process is accelerated and the conductor lifetime decreases. The current densities of  $\ge 10^6 \, \text{A/cm}^2$  are

desirable for the operation of VLSI and ULSI circuits [7]. Therefore, some attention should be paid to this problem.

For the heating of metallization the thermal properties of semiconductor substrate, the insulating layers and package materials including the bond wires are important. From this point of view the high thermal conductivity  $\lambda_{\rm Si} = 1.4 \, {\rm W/cm} \, {\rm K}$  is the great advantage of silicon. It is comparable with the thermal conductivity of metals (e.g.  $\lambda_{\rm Ai} = 2.35 \, {\rm W/cm} \, {\rm K}$ ), being approx. by two orders of magnitude higher than that of  ${\rm SiO}_2$  ( $\lambda_{\rm SiO}_2 = 1.3 \times 10^{-2} \, {\rm W/cm} \, {\rm K}$ ). Therefore, it can be expected that the thickness of  ${\rm SiO}_2$  will influence the heating of metallization considerably.

The above mentioned problem will be more serious in the case of advanced semiconductor structures based on new materials like GaAs or polyimide, which on the other hand possess smaller thermal conductivities.

In this paper the influence of the SiO<sub>2</sub> underlayer on the heating of Al-Cu-Si metallization is studied for two types of experimental structures.

### 2. EXPERIMENTAL DETAILS

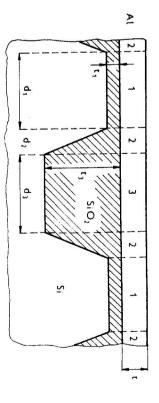

Al-Cu-Si films  $0.6 \,\mu m$  thick were deposited by magnetron sputtering at the substrate temperature  $\leq 150^{\circ}$  C onto thermally oxidized silicon. The composition of the planar magnetron target was Al-4 wt. % Cu-1 wt. % Si. Two types of substrates were used: a) wafers with planar surface and with the constant oxide thickness  $t_{SiO_2} = 1.6 \,\mu m$ ; b) wafers prepared by selective oxidation through a nitride mask with the SiO<sub>2</sub> thickness varying between 1.6 and  $0.04 \,\mu m$ . The "bird beaks" at the boundaries of thick and thin oxide regions were lowered to  $0.3 \,\mu m$  by chemical etching. By neglecting these small bumps the simple model shown in Fig. 1 can be applied in our experimental arrangement. Here  $d_1 + d_2 = d_2 + d_3 = 10 \,\mu m$ ,  $t_1 = 0.04 \,\mu m$ ,  $t_3 = 1.6 \,\mu m$  and  $d_2$  is estimated to be 1  $\mu m$ .

Fig. 1. The simplified model of the sample with varying thickness of the silicon oxide

<sup>&</sup>lt;sup>1)</sup> Institute of Physics, EPRC, Slovak Acad. Sci., 842 28 BRATISLAVA, Czechoslovakia

<sup>2)</sup> Institute of Technical Cybernetics, Slovak Acad. Sci., 842 37 BRATISLAVA, Czechoslovakia

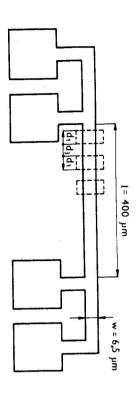

Test conductors with four expanded contacts (Fig. 2) were patterned photolithographically in Al-Cu-Si films on both types of substrates. The length and width of stripes were  $l=400\,\mu\mathrm{m}$  and  $w=6.5\,\mu\mathrm{m}$ , respectively. The conductors were passivated by PE CVD silicon nitride  $0.9\,\mu\mathrm{m}$  thick, deposited at 380° C. They were bonded ultrasonically by aluminium wires and the samples were completed by encapsulating the chips into ceramic packages.

Fig. 2. The conductor on the substrate with varying thickness of the silicon oxide

Due to four contacts the resistivity of conductors can be measured and the samples can be used as self-thermometers for the evaluation of their own temperature

$$9 = 9_a + \Delta 9. \tag{1}$$

Here  $\theta_a$  is the temperature of the ambient (oven, thermostat) and  $\Delta\theta$  is the temperature increase due to Joule heating, which follows from the simple relation  $R = R_a(1 + \alpha\Delta\theta)$ . (R is the resistance of the conductor and  $\alpha$  is the temperature coefficient of resistance, which is measured independently at small current density  $< 10^4 \,\mathrm{A/cm^2}$ .)

The temperature increase  $\Delta \theta$  at  $j > 10^6 \, \text{A/cm}^2$  was measured at a.c. stressing (50 Hz) with the effective current value  $I_{ef} = jtw$ , where t is the metallic film thickness. This procedure must be employed because it was observed that at conventional d.c. stressing the results are influenced by electromigration defect formation during long measuring cycles, caused by the thermal inertia of the samples.

## 3. RESULTS AND DISCUSSION

The resistivity and the temperature coefficient of resistance of conductors under investigation are  $\varrho_{20^{\circ}\text{C}} = 4.7 \,\mu$  Ohm cm and  $\alpha = 2300 \times 10^{-6} \,\text{K}^{-1}$  (for 20 —250° C), respectively. The increase of the temperature  $\Delta \theta$  was measured at  $\theta_a = 180^{\circ}\text{C}$  and  $I_{ef} = 140 \,\text{mA}$  ( $j = 3.6 \times 10^{6} \,\text{A/cm}^{2}$ ).

In the case of the conductor on a planar surface the values  $\Delta \theta = 69-71^{\circ}$ C were obtained with five samples, the mean value being  $\overline{\Delta \theta} = 70^{\circ}$ C and  $\overline{\theta} = 70^{\circ}$ C

In our preceding experiments with similar samples it was shown [4] that the dependence between  $\Delta\theta$  and the power dissipated in the conductor is linear:

$$\Delta \theta = \gamma R(\theta) I_{ef}^2 = \gamma W. \tag{2}$$

Here W is the input power and  $\gamma$  is the slope which did not depend on the ambient temperature in the used interval of  $\theta_a = 30-180^{\circ}$  C. The relation (2) was verified for  $j = (1-4) \times 10^{6}$  A/cm<sup>2</sup> and the values  $\Delta \theta$  were  $\leq 100^{\circ}$  C.

The simple calculation, with the boundary  $Si - SiO_2$  assumed to be the isothermal surface with the temperature  $\theta_a$ , yields

$$\gamma = \frac{\iota_{\text{SiO}_2}}{\lambda_{\text{SiO}_2} l w}.$$

(3)

For our samples  $\gamma = 462 \,\mathrm{K/W}$ . This value can be compared with the experimental one, obtained from the relation (2), where  $\overline{\Delta 9} = 70^{\circ} \,\mathrm{C}$  and R is calculated by means of the resistivity  $\varrho_{250^{\circ}\mathrm{C}} = 7.2 \times 10^{-6} \,\mu\,\mathrm{Ohm\,cm}$ . Then  $W = 145 \,\mathrm{mW}$  and  $\gamma_{\mathrm{exp}} = 483 \,\mathrm{K/W}$ . The difference between both slopes is quite small with regard to the simplified model and to the temperature drops on the chip and the package, respectively.

Measurements of a similar type were performed by Fischer and Neppl [8, 9]. In their papers the input power W and the current induced temperature rise  $\Delta 9$  are related using the quantity  $h = W/lw\Delta 9$ , called heat transfer rate. The exact comparison of these and our results was not possible because not all relevant data were found in papers [8, 9]. It could be only estimated that the results differ less than within the factor of 3.

In the case of conductors on chips with varying SiO<sub>2</sub> thickness the values  $\Delta \theta = 37-39^{\circ}$  C ( $\overline{\Delta \theta} = 38^{\circ}$  C,  $\overline{\theta} = 218^{\circ}$  C) were obtained with five samples. In this case  $\Delta \theta$  represents some average value and the temperature along the conductor fluctuates about this level. It is important to know the amplitude of these fluctuations in order to estimate the temperature gradients in the conductor, which adversely influence the electromigration reliability and lifetime of the metallization. The direct measurement of the temperature distribution was beyond our possibilities, therefore we tried to throw some light upon this problem by approximate calculations at least.

## 4. DISTRIBUTION OF TEMPERATURE ALONG THE CONDUCTOR CROSSING THE REGIONS WITH VARYING SIQ, THICKNESS

We use the model shown in Fig. 1. Here the passivation layer is omited with regard to its thermal conductivity, which is approx. 20 times smaller than that of aluminium [10]. We assume that the temperature at the Si — SiO<sub>2</sub> boundary equals  $\mathfrak{G}_a$ .

The analysis of the chosen model is based on the heat balance of three Al-Cu-Si segments according to Fig. 1. The mean temperatures of the individual conductor segments i=1,2,3 are  $\theta_i$ , Joule heats dissipated in the corresponding parts of the conductor are  $Q_D$ , and  $P_i$  represent the heats conducted perpendicularly through the oxide into the substrate. Finally,  $T_{21}$  and  $T_{32}$  are heats exchanged between the indicated segments. Further, we assume a two-dimensional configuration, i.e. the constant temperature across the width of the conductor.

In thermal equilibrium  $T_{12}=-T_{21}$  and  $T_{23}=-T_{32}$  and the heat balance in each segment gives

$$Q_1 = P_1 - 2T_{21}, (4)$$

$$Q_2 = P_2 + T_{21} - T_{32}, (5)$$

$$Q_3 = P_3 + 2 T_{32}. (6)$$

The mean distances of segments from the Si — SiO<sub>2</sub> boundary are

$$l_1 = t_1 + \frac{t}{2},\tag{7}$$

$$l_2 = \frac{t_1 + t_3 + t}{2},\tag{8}$$

$$l_3 = t_3 + \frac{t}{2}. (9)$$

Dissipated Joule heat is given by

$$Q_i = \frac{\varrho(\vartheta_i) I_{\vartheta_i'}^2 d_i}{wt} \tag{10}$$

and for the conducted heats  $P_i$ ,  $T_{21}$ ,  $T_{32}$  one can use the linear estimates

$$P_i = \frac{\lambda_{\text{SiO}_2}(\theta_i - \theta_o) d_i w}{l_i}, \tag{11}$$

$$T_{21} = \frac{2\lambda_M(\theta_2 - \theta_1) wt}{d_1 + d_2},$$

(12)

$$T_{32} = \frac{2\lambda_M(9_3 - 9_2)wt}{d_2 + d_3},\tag{13}$$

where  $\lambda_M$  is the thermal conductivity of the metallization.

Using the experimental values  $\lambda_M = \lambda_{A1}$ ,  $\varrho(\vartheta_i) = \varrho(218^{\circ}\text{C}) = 6.85 \,\mu$  Ohm cm (here the small temperature differences between resistivities of individual segments were omited) and others mentioned above, we evaluate the segment temperatures:  $\vartheta_1 - \vartheta_a = 22.5^{\circ}\text{C}$ ,  $\vartheta_2 - \vartheta_a = 28^{\circ}\text{C}$ ,  $\vartheta_3 - \vartheta_a = 32^{\circ}\text{C}$ . The experimental value  $\Delta \vartheta = 37$ —39°C (chap. 3) can be compared with the

The experimental value  $\Delta \theta = 37-39^{\circ}$  C (chap. 3) can be compared with the calculated mean temperature increase of the conductor. With regard to the predominant influence of segments 1 and 3 this quantity can be expressed as  $(\theta_1 + \theta_3)/2 - \theta_a = 27.25^{\circ}$  C. Hence, the agreement is quite good, having in mind the temperature drop on the semiconductor and the ceramic parts of the sample.

According to our calculations the temperature differences of  $\approx 10 \,\mathrm{K}$  and the temperature gradients  $2(9_3 - 9_1)/(d_1 + d_3 + 2d_2) \approx 10^4 \,\mathrm{K/cm}$  are to be expected in the investigated conductors. These values are quite high and they are comparable with those reported in ref. [6]. Consequently, the electromigration voids and hillocks can form in the places where the thickness of the oxide changes abruptly.

In our calculations the quantity  $\lambda_{M}=\lambda_{A1}$  was used, as the exact value of  $\lambda_{A1-C1-S1}$  and its temperature dependence could not be measured. Using the Wiedemann—Franz law it can be estimated that  $\lambda_{A1-C1-S1}$  equals approx. 1.7 W/cm K at 218° C. However, even this shift of thermal conductivity does not influence the calculated temperatures markedly. The temperatures  $\theta_i$  are slightly higher, the increase being  $\leq 3.5^{\circ}$  C, and  $(\theta_1 + \theta_3)/2 - \theta_a \approx 29^{\circ}$  C. The differences correlate with decreased heat exchange between the segments.

### 5. CONCLUSIONS

It was shown that the increase of the temperature of metallization of silicon devices due to the dissipation of the Joule heat is influenced first of all by the thickness of the SiO<sub>2</sub> underlayer, which is a bad heat conductor. On the other hand, the thermal conductivity of the silicon substrate is high. Therefore, the heating of metallization can be estimated with sufficient accuracy by the use of very simple models and procedures, which yield the distribution of temperature in two-dimensional and two-layered structures. Further, it follows from the paper that attention should be devoted to the temperature activated degradation processes and the operational stability of tomorrow's semiconductor devices and circuits with narrow conductors, carrying high current densities.

#### REFERENCES

- [1] D'Heurle, F. M., Ho, P. S.: In: Thin Films-Interdiffusion and Reactions. (Eds. J. M. Poate, K. N. Tu, J. W. Mayer). J. Wiley, New York 1978, p. 243.

- Hartsough, L. D., Denison, D. R.; Solid State Technol., 22 (1979), No. 12, 66

- [2] Hartsough, L. D., Denison, D. R.: Solid State Technol., 22 (1979), N. [3] Vaidya, S., Fraser, D. B., Lindenbger, W. S.: J. Appl. Phys. 51 (1984), Luby, S., Roman, P., Barna, P. B.: Elektrotechn. čas., 35 (1984), 298.

[5] Luby, S., Lobotka, P.: Elektrotechn. čas. 30 (1979), 409. Vaidya, S., Fraser, D. B., Lindenbger, W. S.: J. Appl. Phys. 51 (1980), 4475.

- [6] Luby, Š. et al.: Slabopr. obzor 40 (1979), 201.

[7] Ghate, P. B.: Solid State Technol. 26 (1983), No. 3, 113.

[8] Fisher, F.: Siemens Forsch-u. Entwickl. Ber. Bd. 13, No 1, Springer Verlag 1984, p. 21.

[9] Fischer, F., Neppl, F.: Proc. 22nd Annual Int. Reliability Symp. 1988, IEEE, New York 1984, p. 190.

- [10] Wilson, A. M.: Thin Solid Films 23 (1981), 145.

Accepted for publication October 13th, 1988 Received July 29th, 1988

## ВЛИЯНИЕ НИЖНЕГО СЛОЯ SIO, НА ДЖОУЛЕВСКОЕ НАГРЕВАНИЕ Al-Cu-Si МЕТАЛЛИЗАЦИИ КРЕМНИЕВЫХ ПРИБОРОВ

тока могут существенно повлиять на действие и надежность полупроводниковых приборов го на два порядка ниже, чем у кремния. Результаты демонстрируют, что высокие плотности влияет главным образом толщина нижнего слоя SiO2, температурная проводимость котороли. Соответствие довольно хорошее; это подсказывает, что на нагревание в металлизации зультаты сравнены с расчетами распределения температуры, основанного на простой модеокисля, где толщина была не больше, чем в первом случае, среднее значение повышения температуры (флуктуирующей вдоль проводника), было 37—39°С. Экспериментальные регреванием, достигало 70°C для первого типа подложки. Для подложки с переменной толщиной няющейся толщиной SiO<sub>2</sub>. Проводники загружались высокой плотностью тока (  $> 10^6 \, \text{A/cm}^2$ ). нетронным напылением на окисленные кремниевые подложки как с постоянной, так и с ме-При этих условиях повышение температуры проводников, обусловленное джоулевским на-Экспериментальные проводники приготовылись в Al-Cu-Si пленках, нанесенных маг-